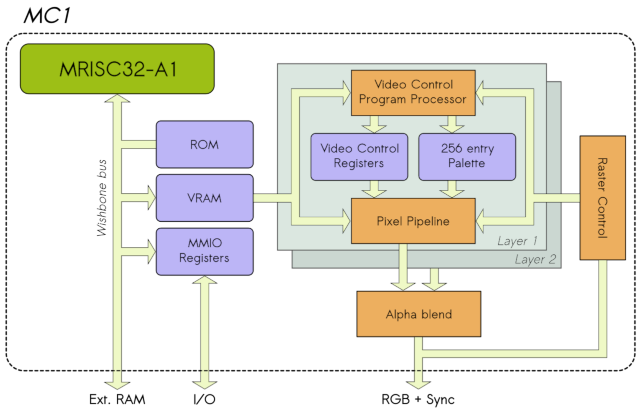

Here is a short report on the current state of my MC1 project, which is an SoC design for FPGA:s.

The MC1 is a custom computer that is mainly used for testing and proving the MRISC32 ISA. Currently the main features of the computer are:

- It is based around the MRISC32-A1 soft CPU, running at 100+ MHz.

- It has fairly powerful programmable, dual layer video logic that can output a 1920×1080@60 video signal.

- It has on-FPGA ROM and video RAM.

Here is a short demo running on an Intel Cyclone V FPGA:

The computer architecture

The MC1 is implemented in portable VHDL and should be fairly simple to port to most FPGA:s (with sufficient hardware capabilities, such as dual ported BRAM).

The most interesting part of the MC1 (except for the MRISC32-A1) is probably the video logic that makes it possible to mix and match pixel formats, palettes, resolutions and blending modes in a single video frame, thanks to the Video Control Program Processor (a programmable, pipelined raster-synchronized processor, similar to the Amiga Copper).

The CPU

The CPU of the MC1 is a MRISC32-A1, which is a single issue, in order, pipelined implementation of the MRISC32 ISA. The ISA has been covered in some previous blog posts. Many of the CPU features were used in the demo.

For instance, in the retro/raster part the 4×8-bit saturating instructions were useful for RGBA color calculations:

Another useful feature is the 2×16-bit floating-point instructions that came into use when computing the perspective division for the 3D star field (there are 32768 stars in the scene):

The MRISC32 vector instructions were used for accelerating the Mandelbrot fractal renderer:

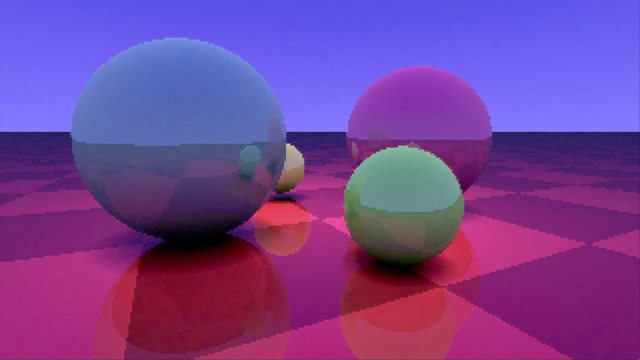

The one part that was written almost exclusively in pure C++ was the ray tracer. Of course the 32-bit floating-point support of the MRISC32-A1 CPU made it possible to achieve decent performance (about 2 FPS at 320×180).

The MRISC32 ISA

The best part of making your own ISA is that you can design it just the way you like it, and after having used it for some time I can say that it actually turned out quite well: I really prefer programming for the MRISC32 ISA, compared to other ISA:s that I have used (ARMv7, RISC-V, x86, 68k, MIPS, etc).

On the other hand, the worst part of making your own ISA is that you have to make your own tool chain ports. I have spent way too much time on the GNU GCC MRISC32 back end, for instance, and in hindsight it might have been better to start with an LLVM back end instead.

Future plans

The next few steps are:

- Add an SDRAM controller to take advantage of on-board memory (e.g. the board I am using has 64 MB of SDRAM). This will enable running more advanced programs, such as DOOM.

- Add SD-card I/O. This will make it possible to load programs into RAM instead of running them from the ROM (rebuilding the FPGA bitstream to update a program is kind of tedious).